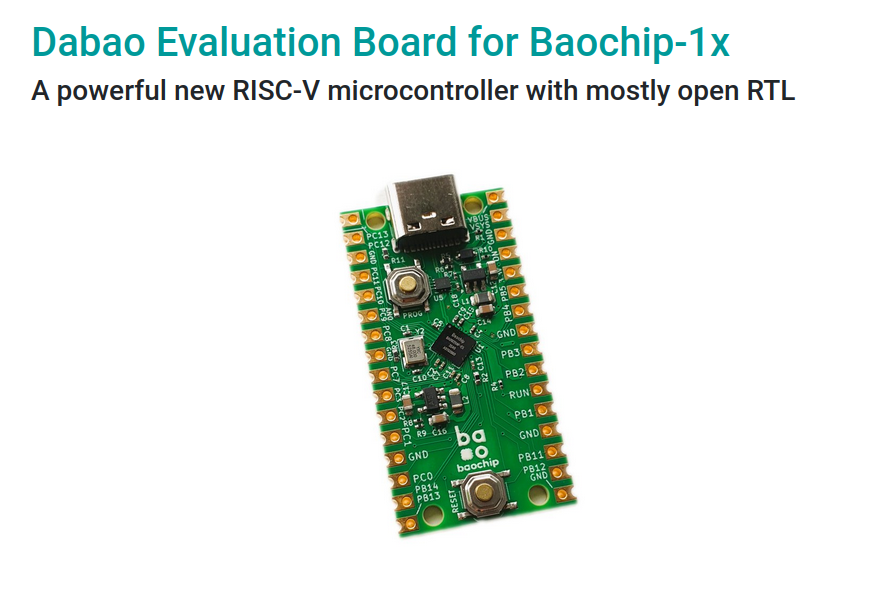

Die große Politik geht weiter: SiTime kauft die Timingsparte von Renesas, während Microchip im Automotivebereich zwecks Förderung von SPE mit Hyundai partnert. STMicroelectronics läuft Amazon hinterher, während Transmille voll auf die Bedürfnisse von Kalibrationslaboren setzt. Außerdem gibt es Software- und Hardwareupdates und ein QuecTel-Evaluationsboard…

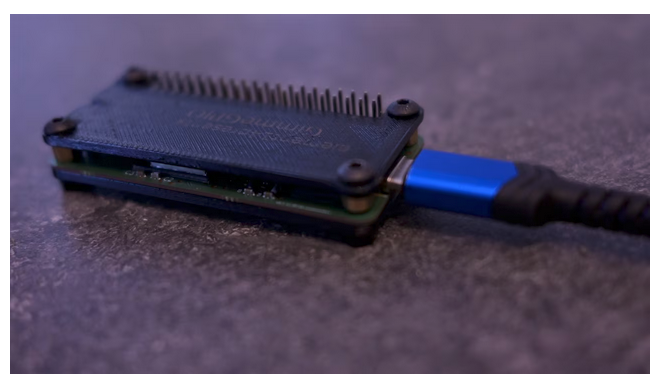

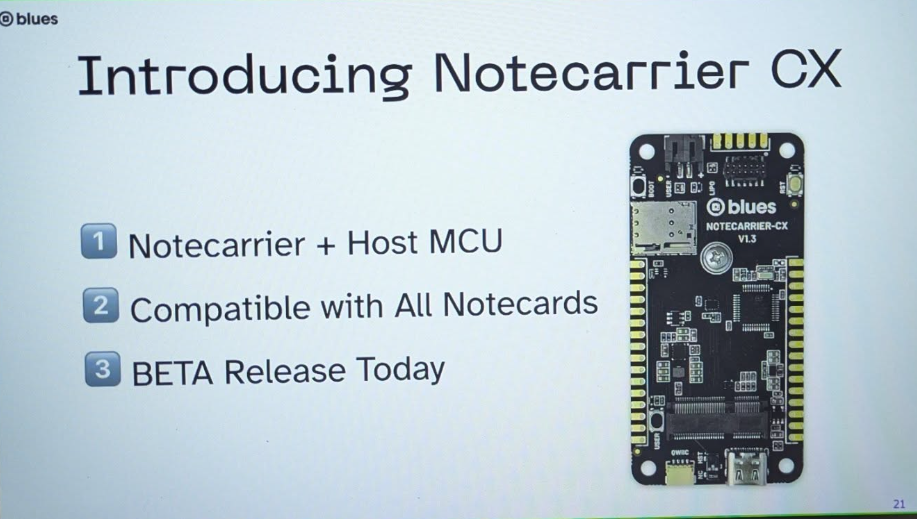

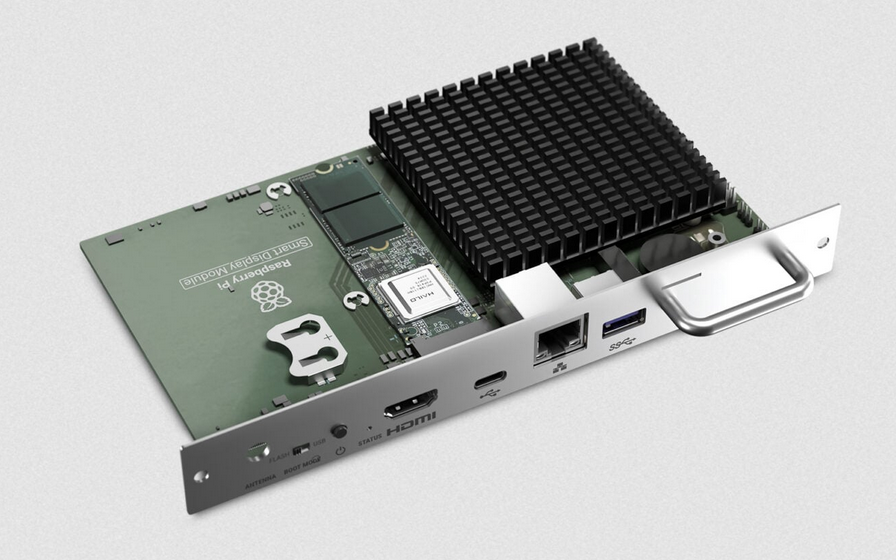

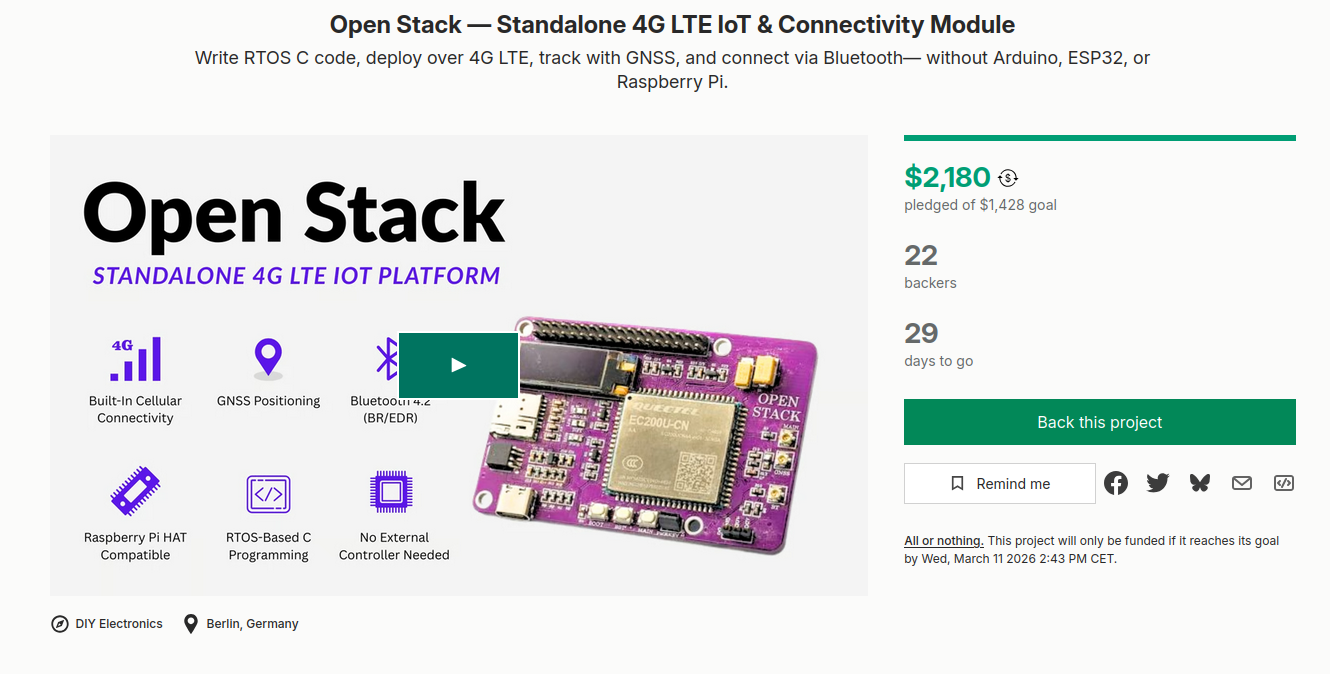

Open Stack – QuecTel ohne Arduino

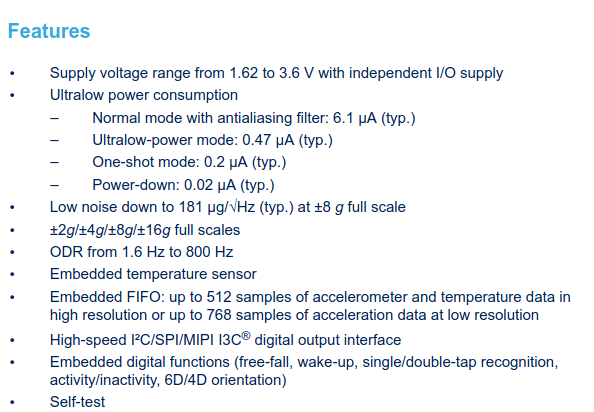

Der Funkmodulhersteller QuecTel bietet seit einiger Zeit verschiedene SDKs an, die die Programmierung der diversen Module in Python oder FreeRTOS erlauben. Ziel ist, Funksysteme zu realisieren, die ohne Coprozessor auskommen.

Nun steht erstmals eine Platine ante Portas, deren Lebenssinn die Realisierung derartiger Projekte ist. Weitere Informationen finden sich bei KickStarter…

Bildquelle: https://www.kickstarter.com/projects/k-dave/open-stack

STMicroelectronics Stellar P3E – AI-Microcontroller für den Automotivebereich

Mikrocontroller mit AI-Beschleunigung sind per Se nichts wirklich neues. STMicro lanciert nun eine neue Variante der für Fahrzeuge vorgesehenen Stellar-MCUs, die – für diesen Bereich erstmals – einen AI-Beschleuniger mitbringt:

1 |

Ein herausragendes Merkmal des Stellar P3E ist sein integrierter ST Neural-ART Accelerator™ für Echtzeit-KI-Effizienz – damit ist er die erste MCU mit eingebettetem neuronalen Netzwerkbeschleuniger für die Automobilindustrie. Angetrieben von dieser dedizierten neuronalen Verarbeitungseinheit (NPU) mit einer fortschrittlichen Datenflussarchitektur für KI-Workloads und kombiniert mit seinen umfangreichen Sensorfähigkeiten, ermöglicht der P3E intelligente Sensorik, die die Tür für neue Anwendungen wie virtuelle Sensoren öffnet. |

2 |

|

3 |

. . . |

4 |

Der Produktionsstart des Stellar P3E ist für das vierte Quartal 2026 geplant. |

Bildquelle: STMicroelectronics

Zu den allgemeinen Spezifikationen vermeldet ST dann folgendes:

1 |

• 500 MHz Arm® Cortex®-R52+ Kerne mit der höchsten CoreMark-Punktzahl in seiner Klasse – über 8.000 Punkte. |

2 |

• Split-Lock-Architektur, die Designern ermöglicht, das Gleichgewicht zwischen funktionaler Sicherheit und Spitzenleistung zu optimieren. |

3 |

• Offene Arm-Architektur, die eine große globale Entwicklergemeinschaft für beschleunigte Innovation nutzt. |

4 |

• Umfangreiche I/O- und analoge Fähigkeiten unterstützen vielfältige Funktionen, einschließlich fortschrittlicher Motorsteuerung für verbesserte Fahrzeugdynamik. |

Microsoft MAIA 200 – vom Design eines effizienten AI-Beschleunigers

Im Hause Microsoft steht ein neuer AI-Beschleuniger am Start, der der hauseigenen Azure-Division beim effizientestmöglichen Anbieten der diversen cloudbasierten Dienste helfen soll.

Bildquelle: https://blogs.microsoft.com/blog/2026/01/26/maia-200-the-ai-accelerator-built-for-inference/?

Für Elektroniker interessant ist besonders die Beschreibung, die auch auf “allgemeine Probleme” beim Chipdesign eingeht – eine relevante Passage findet sich unten:

1 |

Crucially, FLOPS aren’t the only ingredient for faster AI. Feeding data is equally important. Maia 200 attacks this bottleneck with a redesigned memory subsystem. The Maia 200 memory subsystem is centered on narrow-precision datatypes, a specialized DMA engine, on-die SRAM and a specialized NoC fabric for high‑bandwidth data movement, increasing token throughput. |

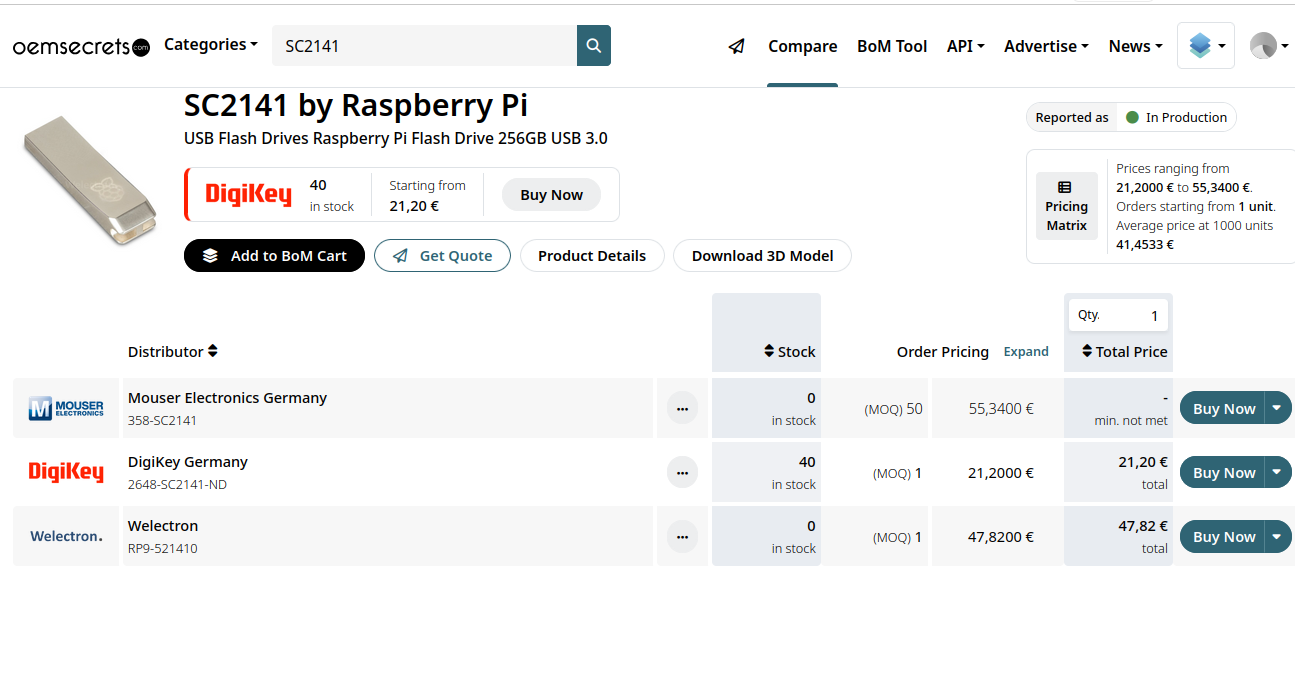

Neue Raspberry Pi 4B-Version mit geändertem Speicherlayout

Aufgrund der Speicherkrise gibt es eine neue Variante des RPi 4B, die mit zwei Speicherchips arbeitet. Laut der unter https://pip-assets.raspberrypi.com/categories/560-pcn/documents/RP-009677-PC-1-PCN%2045_%20Raspberry%20Pi%204%20Dual%20RAM%20variant.pdf bereitstehenden PCN müssen Nutzer darauf achten, eine aktuelle Version des Bootloaders zu verwenden:

1 |

This new product revision is supported in bootloader versions from 9 Jan 2026 onwards. (pieeprom-2026-01-09.bin) |

Texas Instruments MSPM33C321A – Leaking als PR-Mittel für Mikrocontroller

Im Bereich Handcomputer hat sich das inoffizielle Auslassen von Informationen über Produkte seit Jahr und Tag als PR-Methode gut etabliert. Texas Instruments experimentiert nun – wie in der Abbildung gezeigt – ebenfalls mit der Vorgehensweise.

Bildquelle: https://www.linkedin.com/feed/update/urn:li:activity:7415373888030720001/

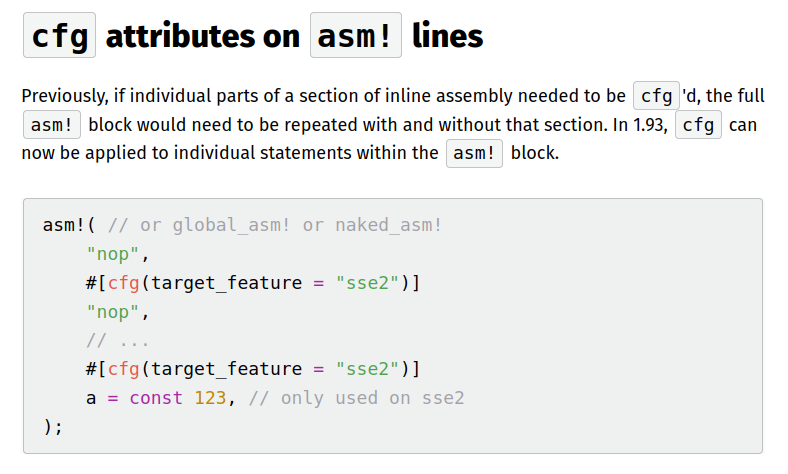

Linux 6.19 verfügbar, 7.0 folgt

Im Hause Thorvalds gibt es eine neue Kernelversion, die – humoristisch – mit einem kleinen Seitenhieb auf das in den USA stattfindende Sportevent angekündigt wurde:

1 |

No big surprises anywhere last week, so 6.19 is out as expected – just as the US prepares to come to a complete standstill later today watching the latest batch of televised commercials. The betting man would expect them all to be AI-generated, but maybe some enterprising company decides to buck the trend? Doubtful, but there’s always a slight chance. |

2 |

But for anybody outside the US, maybe taking the newest kernel out for a spin instead is an option? |

CNX bietet wie immer unter https://www.cnx-software.com/2026/02/09/linux-6-19-release-main-changes-arm-risc-v-and-mips-architectures/ eine umfassende Liste der diversen für Embedded-Entwickler potentiell relevanten Neuerungen an.

Interessant ist ausserdem, dass die nächste Version – auf 7.0 hörend – die Integration von Rust nicht mehr als Experiment, sondern als finalisiert ankündigt. Weitere Informationen zu sonstigen Änderungen finden sich unter https://www.phoronix.com/news/Linux-7.0-Is-Next und https://www.phoronix.com/news/Linux-7.0-Rust.

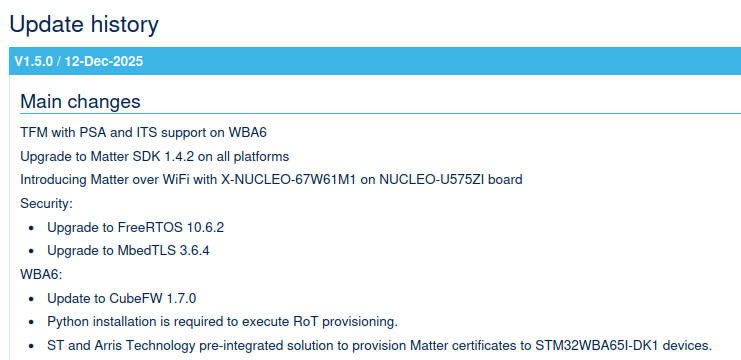

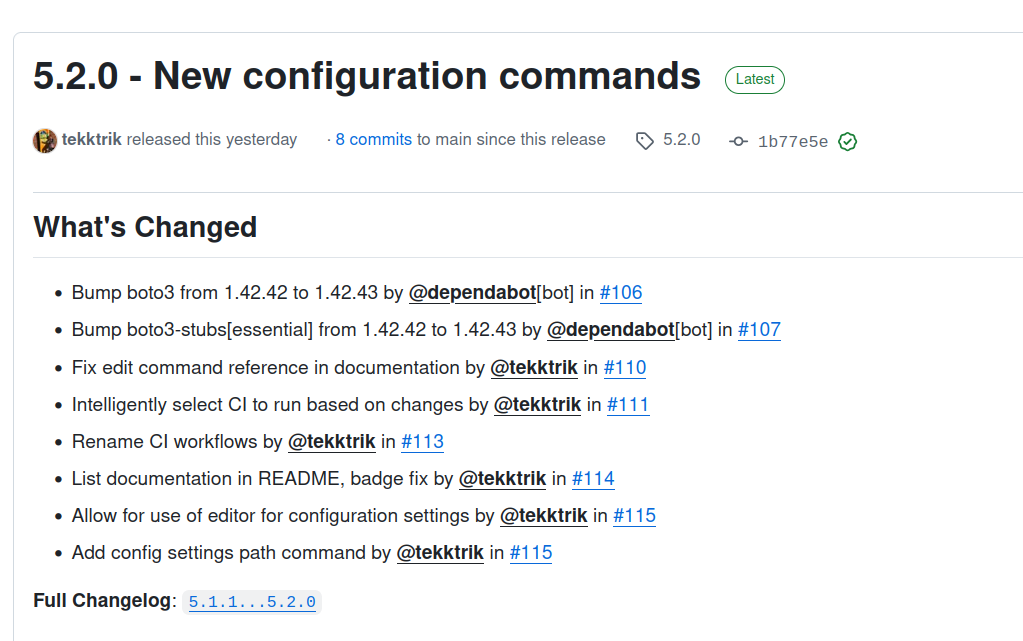

Circfirm-Update verfügbar

Wer CircuitPython-Boards mit neuer Firmware auszustatten gedenkt, kann dies bequem über das dafür vorgesehene Kommandozeilenwerkzeug circfirm bewerkstelligen:

1 |

# Install a version of CircuitPython to a connected board

|

2 |

circfirm install 8.0.0 |

Nun gibt es eine neue Version des Programms; die Änderungen sind in der Abbildung zusammengefasst.

Bildquelle: https://github.com/tekktrik/circfirm/releases/tag/5.2.0

Transmille: Fokus komplett auf Kalibrationslabore

Die britische Transmille – als Nachfolger der Solartron Schlumberger fertigt man hochpräzise Multimeter (und seit dem Fehlschlag mit dem SI7063 keine Desktop-Multimeter mehr) – beteiligt sich am Trend der Spezialisierung im Messtechnikbereich.

In einem vor wenigen Tagen veröffentlichten Video zeigt man eine Programmsuite, die sich komplett um die Bedürfnisse von Kalibrationslabore kümmert – der Funktionsumfang reicht von Messwerterfassung bis zur Erzeugung der Honorarnote und der Versandlabels.

Bildquelle: https://www.youtube.com/watch?v=uYJA5orU4XY

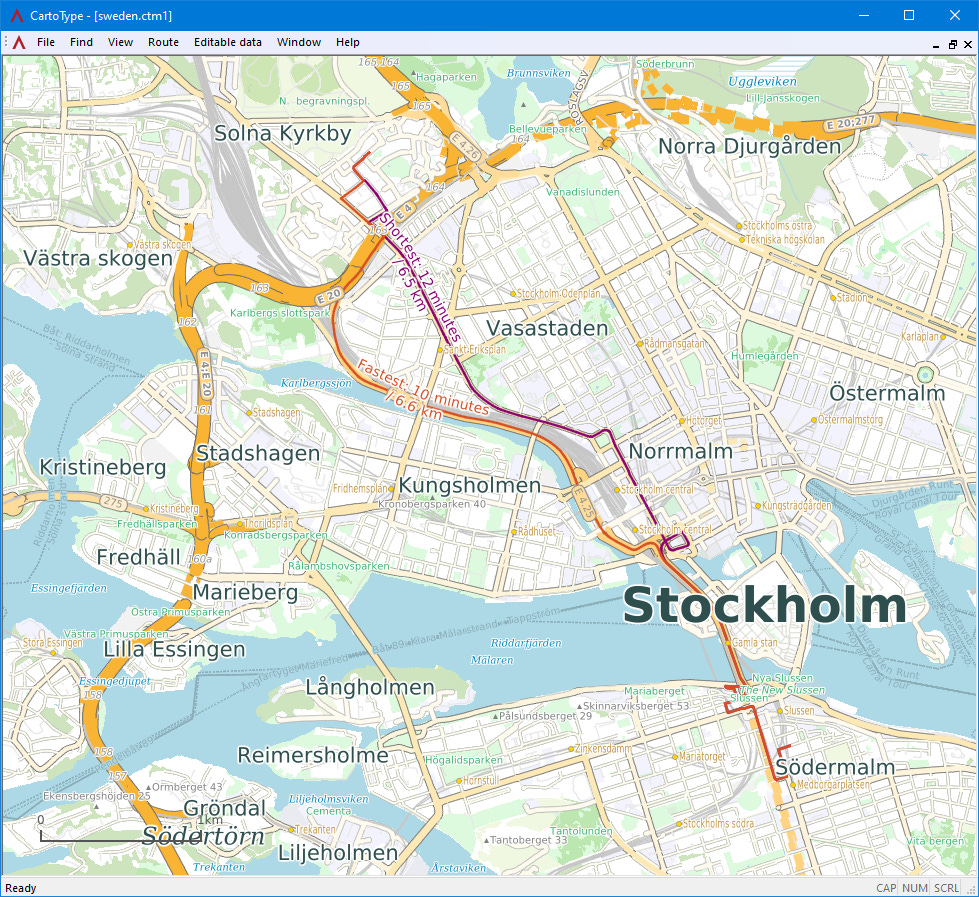

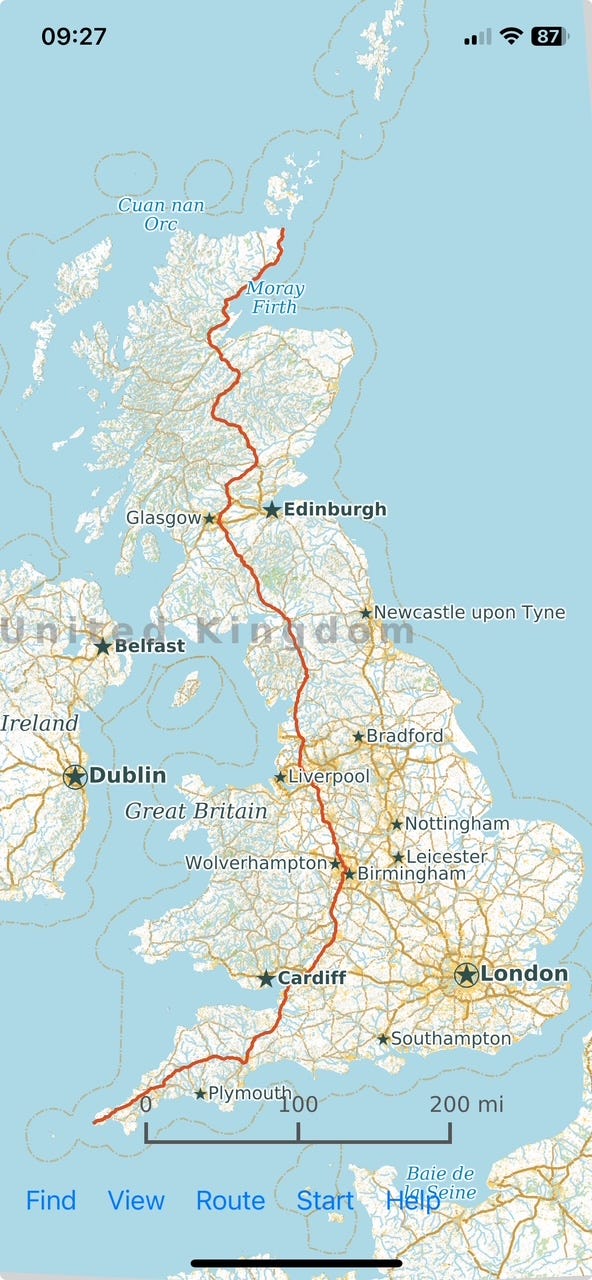

CartoType 9.4 reduziert Speicherbedarf und erleichtert Android-Integration

In Sachen europäischer Unabhängigkeit von Big Tech gibt es ein kleines Update – die neueste Version des Mapping-Frameworks bringt die folgenden Detailverbesserungen mit:

1 |

Upgrading is easy. The public API is identical to 9.2, apart from terrain heights now being returned as floating-point numbers instead of integers. |

2 |

The main change is reduction of run-time RAM use by up to half, and better performance resulting from some refactoring of file and route data caching. |

3 |

Android users can take advantage of a new way of loading maps, style sheets and fonts directly from asset archives (for example, from inside APK files), where they are stored in zip-encoded form. |

4 |

--- via https://www.cartotype.com/developers/documentation/release-notes/release-notes-for-cartotype-9-4?utm |

m5Stack – Pyramidonis’s Prozessrechner

Im Hause m5Stack – eigentlich baut man Evaluationsboards für den ESP32 – zeigt man sich immer für einen Blick über den Tellerrand gewillt. Nun steht ein pyramidenförmiger Prozessrechner ante Portas, der seine Rechenleistung aus einem achtkernigen SoC aus dem Hause Axera bezieht.

Bildquelle: https://s.click.aliexpress.com/e/_c4NClRnp

Wer 50 Euro mehr investiert, kann in der Theorie auch eine Variante mit 8GB RAM bestellen – zum Zeitpunkt der Abfassung dieser Meldung ist diese allerdings ausverkauft. Fraglich ist für den Autor die Motivation: ein Schelm, wer denkt, dass man Erfahrungen im Design von Evaluationsboards für MPUs zu sammeln sucht.

Olimex HoT als preiswerte Alternative zu Home Assistant und Co

Im Hause Olimex arbeitet man daran, ein eigenes Gatewaysystem auf Basis von OpenWRT zu entwickeln. Lebenssinn des Systems ist die “Sammlung von Daten”, die auf ESP32-basierten Systemen anfallen.

Weitere Informationen finden sich unter https://www.cnx-software.com/2026/02/06/olimex-hot-aims-to-be-lightweight-easier-to-use-alternative-to-home-assistant/.

SiTime kauft Timingsparte von Renesas

Der Million-Monkey-Effekt ist im Elektronikbereich stark. Wenige Tage nach der letzten Welle von Übernahmen greift die SiTime zu – als Ziel hat man die Timing-Sparte von Renesas auserkoren.

Interessant ist, dass die neue Division einen Gutteil des Gesamtumsatzes der kombinierten Firma ausmachen soll:

1 |

Rajesh Vashist, chairman and CEO of SiTime, said, “This acquisition is a monumental milestone toward fulfilling our vision to transform the timing market and solve our customers’ toughest timing challenges. With Renesas’ timing business, we will increase our clocking portfolio by more than 10x and extend our reach in the fastest growing applications in the timing market, including comms, enterprise and datacenter. Notably, these applications are expected to represent more than 60% of SiTime’s revenue, post-acquisition. We are confident that the acquisition will deliver exceptional value for our shareholders as we build on our strong record of financial performance as underscored by our 2025 results announced today.” |

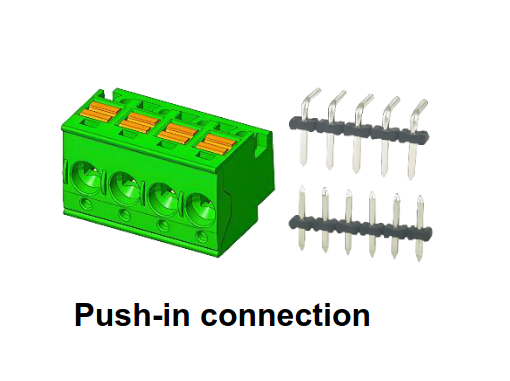

Microchip x Hyundai zwecks Verbreitung von Single Pair Ethernet im Automobilbereich

Der Siegeszug der Ethernet-Technologie ist spätestens seit dem Ende der “Wefzerei” um den korrekten Single Pair Ethernet-Stecker nicht mehr aufzuhalten. Microchip und Hyundai gehen nun eine Kooperation ein:

1 |

Microchip Technology (Nasdaq: MCHP) today announced a collaboration with Hyundai Motor Group (HMG) to explore the adoption of advanced in-vehicle network solutions based on 10BASE-T1S Single Pair Ethernet (SPE) technology. This cooperation effort is intended to support the development of more efficient, reliable and scalable vehicle architectures that meet the evolving demands of future mobility. |

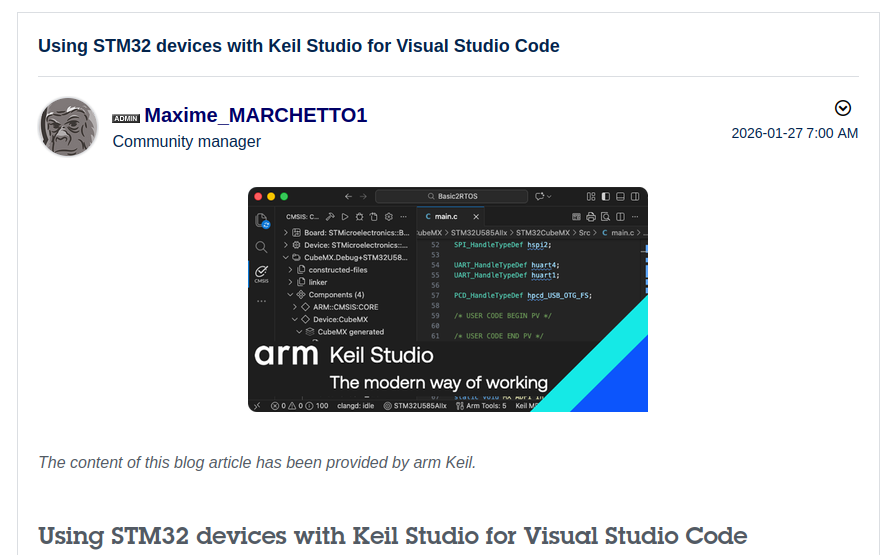

STMicroelectronics partnert mit Amazon Web Services (aka FreeRTOS is us)

Wer mit Microsoft im Embeddedbereich zusammenarbeitet, arbeitet am eigenen Untergang – die Kadaver von Palm, Nokia, Sendo und GHI warnen mahnend am Horizont.

Im Hause STMicroelectronics setzte man einst auf FreeRTOS, um nach der Übernahme von ThreadX durch Microsoft eine Partnerschaft mit Big M einzugehen. Nun scheint man wieder den Rückweg anzutreten:

1 |

Jean-Marc Chery, ST President & CEO, commented: "This strategic engagement establishes ST as an important supplier to AWS and validates the strength of our innovation, proprietary technology portfolio, and proven manufacturing-at-scale capabilities. Our advanced semiconductor solutions will directly power AWS's next-generation infrastructure, enabling their customers to push the boundaries of AI, high-performance computing, and digital connectivity. This collaboration positions us ideally for further scale-up across multiple market segments, from data center infrastructure to AI connectivity, positioning ST at the center of the AI revolution." |

Lesestoff – von der Euroumstellung in Bulgarien

Wer es noch nicht weiss: Bulgarien ist nun Mitglied der Eurozone. Für dort ansässige Firmen oder Investmentvehikel gibt es einiges zu beachten, was Schönherr unter https://mailchi.mp/schoenherr.eu/contentunfair-trading-practices-in-serbia-a-new-legal-framework-inspired-by-eu-law-5238748?e=0c4 zusammenfasst.

Lesestoff, 2 – von der Geschichte der DRAM-Fertigung und ihren Problemen

DRAM und der dazugehörende Schweinezyklus sorgen immer wieder für Schlagzeilen. Unter der URL https://newsletter.semianalysis.com/p/memory-mania-how-a-once-in-four-decades?utm_source=post-email-title&pub= findet sich ein durchaus interessanter Bericht, der die Geschichte der Fertigung von Arbeitsspeicher beleuchtet.

Zuerst erschienen bei Mikrocontroller.net News

Quelle: Weiterlesen