Wie Jimmy Saville für British Rail vom „Age of the Train“ sprach, erzählt die heutige News-Meldung (fast) nur vom Voranschreiten der RISC/V-ISA. Neben politischen Aktivitäten im Bereich der Unterstützung von RISC/V gibt es auch einen Prozessrechner, der dank seines RISC-V-Prozessors für die Zusammenarbeit mit dem chinesischen die DeepSeek-Modell optimiert sein soll. Außerdem stehen Module auf Basis von ESP32-P4 und ESP32-C5 (!!!) zum Verkauf.

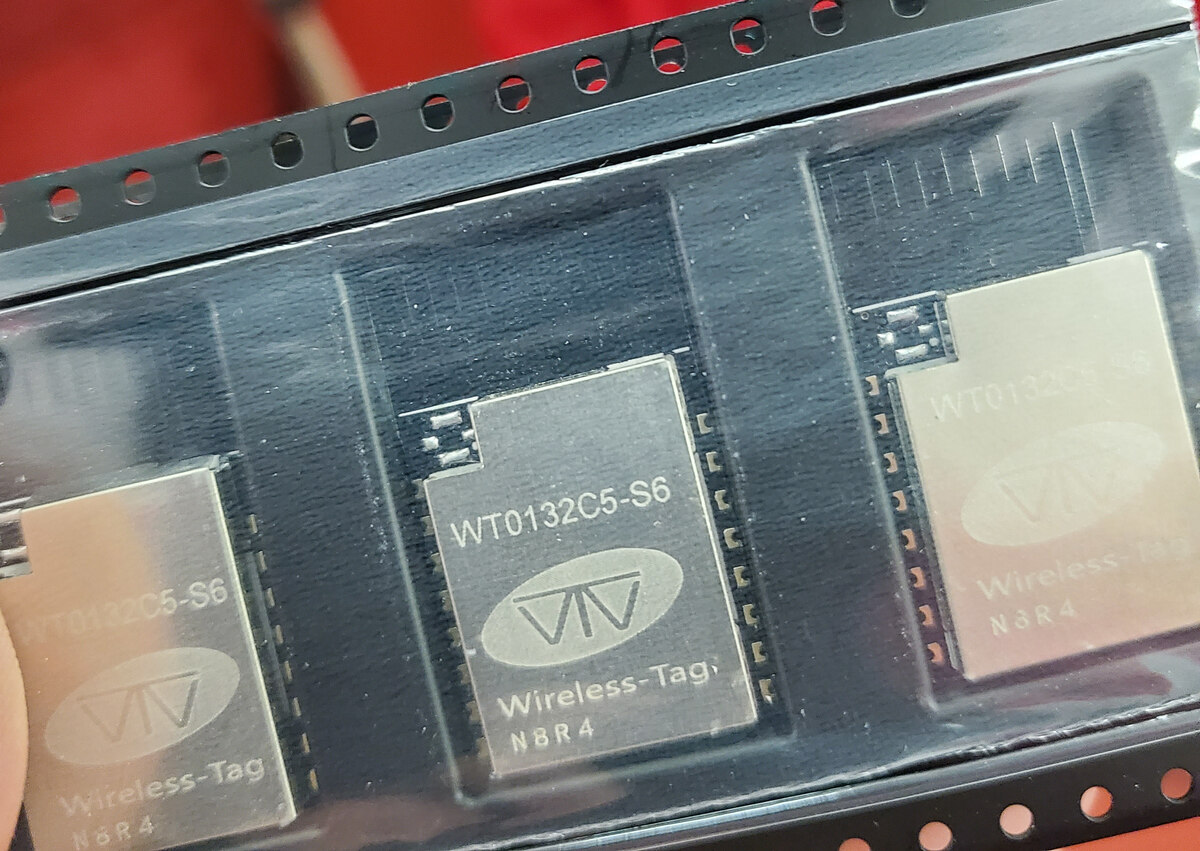

Module auf Basis von ESP32-C5 und ESP32-P4 auf AliBaba

Espressifs neueste Lütten sind derzeit vergleichsweise schwer erhältlich – der C5 ist gar nicht erhältlich, während der P4 beispielsweise am Olimex-Board (siehe https://youtu.be/GUgjmGQvI7c) kaufbar ist.

Espressifs wichtigster chinesischer Distributor Wireless-Tag hat seit einiger Zeit diesbezügliche Module im Handel. Der Autor erwarb einige davon, und hat sie – siehe Abbildungen – im Labor.

Bildquelle, beide: Tamoggemon Holding k.s.

Eine Anfrage bei Wireless-Tag ergab, dass das Unternehmen die Module auf Wunsch auch nach Deutschland liefert. Für Anfragen wurden die URLs https://www.alibaba.com/product-detail/Wireless-tag-ESP32-P4-SOM-module_1601287297180.html?spm=a2747.product_manager.0.0.594871d2U01ATW und https://www.alibaba.com/product-detail/esp32-esp32-c5-2-4G-5G_1601251918870.html?spm=a2747.product_manager.0.0.594871d2U01ATW angeführt.

Streiks am EmbeddedWorld-Anreisetag

Die Embedded World ist von einem Warnstreik betroffen. In einer von wenigen Stunden ausgesendeten Meldung findet sich die folgende Passage:

1 |

die Gewerkschaft Verdi hat für Montag, 10. März 2025, einen ganztägigen Warnstreik an allen größeren Flughäfen in Deutschland angekündigt. |

2 |

|

3 |

Zu den bestreikten Flughäfen gehören: |

4 |

München, Stuttgart, Frankfurt, Köln/Bonn, Düsseldorf, Dortmund, Hannover, Bremen, Hamburg, Berlin-Brandenburg und Leipzig/Halle. |

5 |

|

6 |

Reisende müssen mit massiven Einschränkungen, Flugausfällen und Verspätungen rechnen. Bitte wenden Sie sich direkt an Ihre Airline, um ggf. Umbuchungen vorzunehmen. Der Flughafen Nürnberg ist nicht betroffen. |

Zu beachten ist, dass sich derartige Warnstreiks im Allgemeinen auch auf Zugverbindungen auswirken – wer noch keine Reservierung hat, hat wahrscheinlich Probleme.

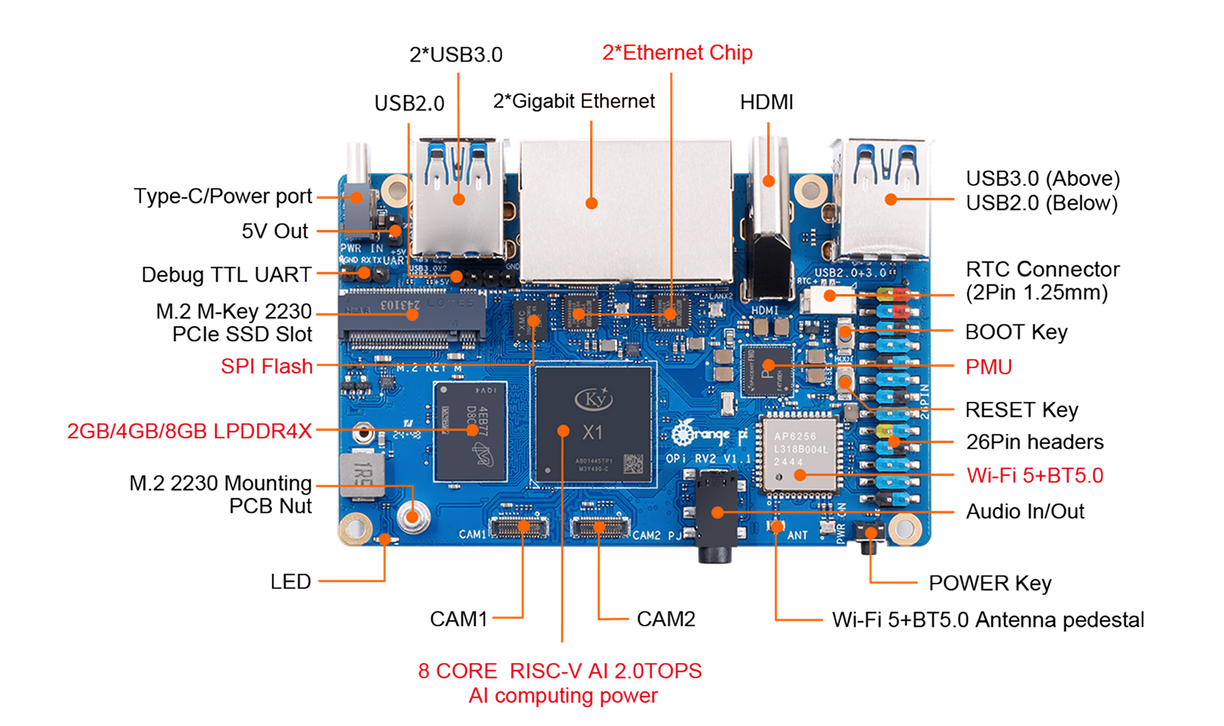

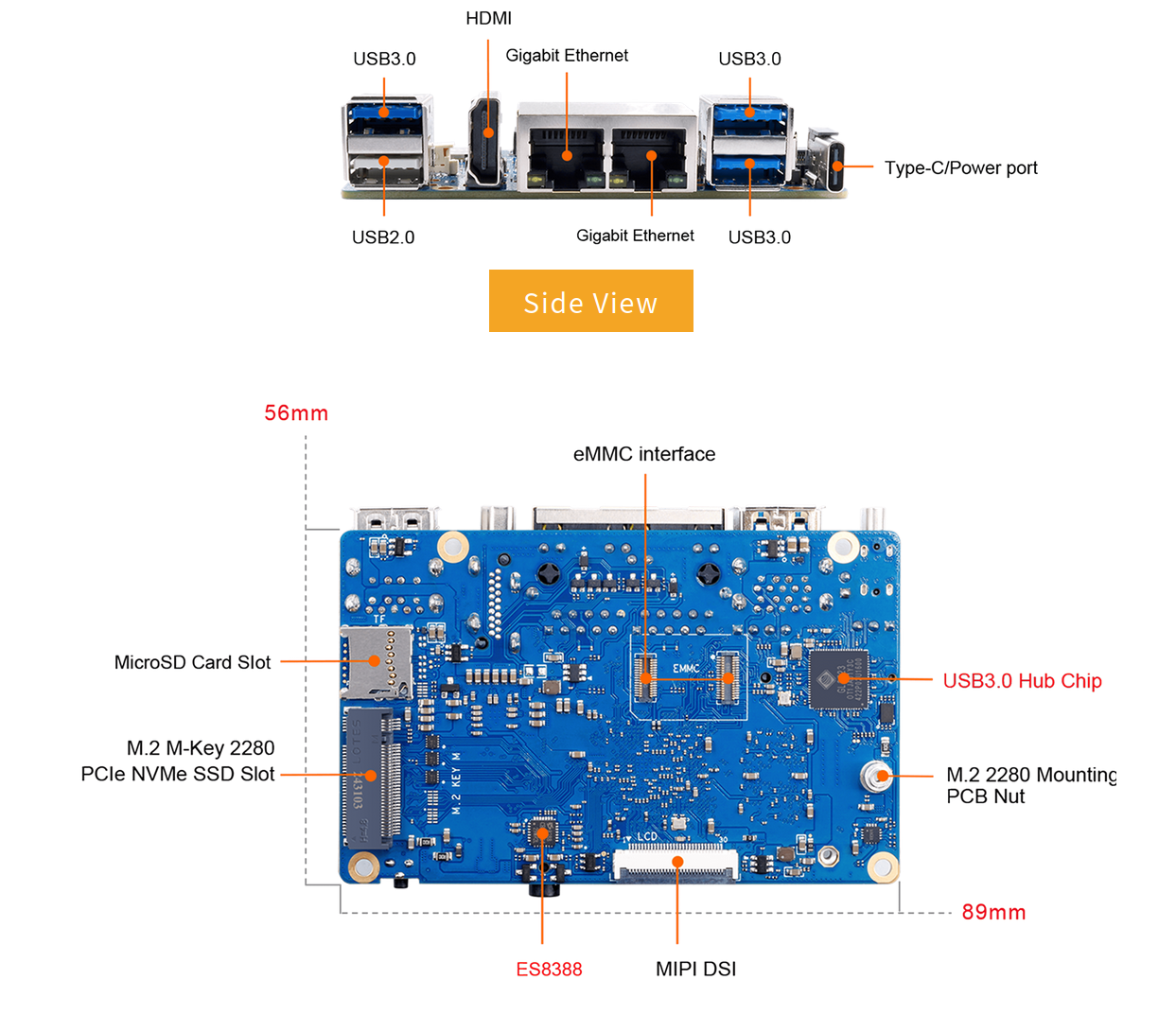

OrangePi RV2 – RISC/V-OrangePi mit Optimierung für AI-Aufgaben.

Obwohl Shenzhen Xunlong long in der Vergangenheit mit den verschiedensten SoCs experimentierte, setzte man im Allgemeinen auf die ARM-Architektur. Mit dem in der Abbildung gezeigten RV2 steht nun eine neue Platine am Start, die ihre Rechenleistung aus einem RISC/V-Kern bezieht.

Bildquelle: http://www.orangepi.org/html/hardWare/computerAndMicrocontrollers/details/Orange-Pi-RV2.html

Bildquelle: http://www.orangepi.org/html/hardWare/computerAndMicrocontrollers/details/Orange-Pi-RV2.html

Als Hauptprozessor kommt ein Ky X1 8-core RISC-V AI CPU zur Verfügung, der von Shenzhen Xunlong mit der Passage 2TOPS AI power als für die Aufgaben der künstlichen Intelligenz besonders geeignet bezeichnet wird.

Interessant ist an der Ankündigung außerdem, dass die neue Platine als besonders gut für die Zusammenarbeit mit dem Deep Seek-AI-Modell optimiert beworben wird.

Bildquelle: http://www.orangepi.org/html/hardWare/computerAndMicrocontrollers/details/Orange-Pi-RV2.html

Infineon: wir werden RISC/V im Automotive-Bereich einsetzen.

Shenzhen Xunlong ist nicht das einzige Unternehmen, das an der quelloffenen ISA Interesse hat. Eine vor wenigen Stunden versendeten Pressemitteilung aus dem Hause Infineon enthält die folgende Passage, die auf die „baldige“ Vorstellung einer RISC/V-Variante der hauseigenen Automotive-Mikrocontroller hindeutet:

1 |

The company will launch a new automotive microcontroller family based on RISC-V within the coming years. This new family will become part of Infineon’s established automotive microcontroller brand AURIX™. It will extend the company’s existing automotive microcontroller portfolio, which is based on TriCore™ (AURIX TC family) and Arm® (TRAVEO™ family, PSOC™ family). The new AURIX family will cover a wide range of automotive applications from entry-level MCUs up to high-performance MCUs beyond what is available in the market today. At Embedded World 2025, Infineon now introduces a virtual prototype enabled by key ecosystem partners. This is a starter kit for Infineon’s partners to begin pre-silicon software development. |

2 |

--- via https://www.infineon.com/cms/en/about-infineon/press/press-releases/2025/INFATV202503-067.html |

In der Pressemeldung finden sich außerdem einige Meldungen, nach denen Infineon versuchen möchte, die Technologie als „offenen Standard“ für Rechnen im Fahrzeugbereich zu etablieren. Da die Embedded World unmittelbar bevorsteht, dürften wir – das Presseteam von Infineon zeigt sich manchmal von der unkooperativen Seite – bald Informationen zum Thema erhalten.

Espressif ESP32-C6 erreicht PSA-L2-Zertifikation

Als ARM die Platform Security Architecture, kurz PSA, im Jahre 2017 einführte, galten die hauseigenen Rechenkerne als „einziges Tier im Stall“. Wohl aus diesem Grund entschied sich ARM, die Deklaration plattformagnostisch zu halten – eine Entscheidung, die wie in der Abbildung gezeigt Konsequenzen entfaltet.

Bildquelle: https://www.espressif.com/en/news/C6_PSA_Level2

Spezifischerweise kündigt Espressif nach folgendem Schema an, dass der hauseigene ESP32-C6, der auf einem RISC/V-Kern basiert, ab sofort gemäß den Richtlinien von PSA2 zertifiziert ist:

1 |

The PSA Certified program, developed in collaboration with industry leaders, provides a framework for confirming the security of IoT devices. Achieving PSA Level 2 certification signifies that the ESP32-C6’s PSA Root of Trust (PSA-RoT) has undergone laboratory evaluation, demonstrating its resilience against scalable software attacks. This certification validates that the ESP32-C6 meets industry-recognized IoT security standards, ensuring robust protection for connected devices. |

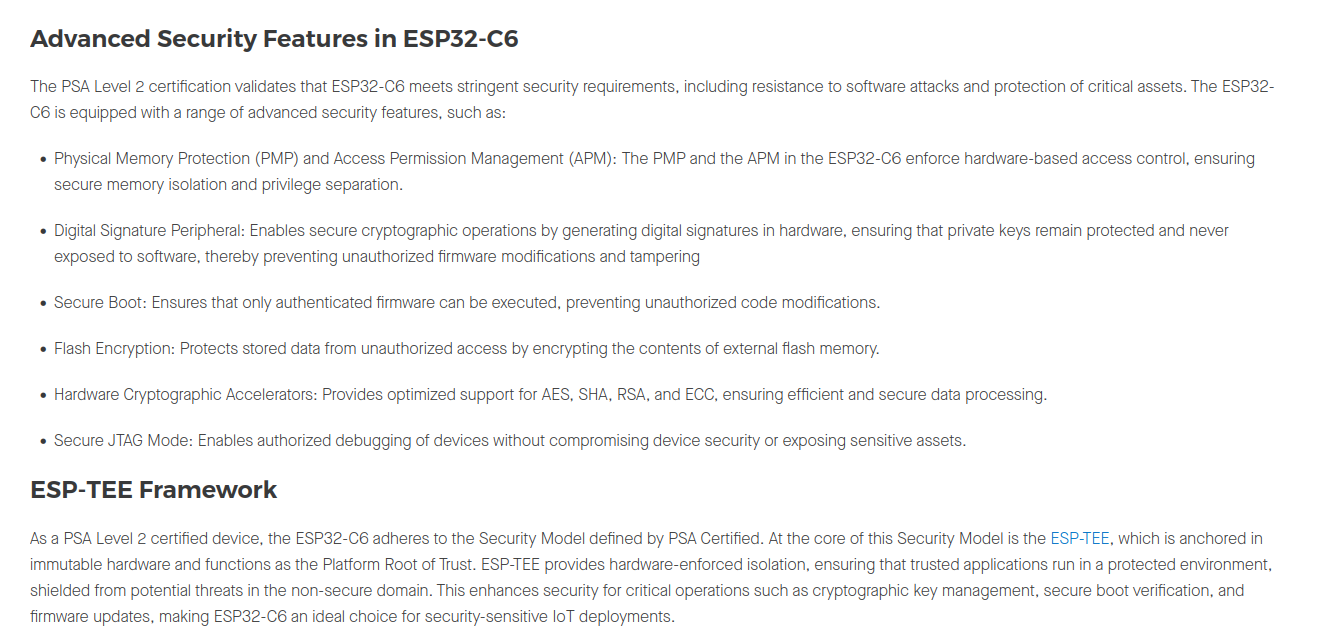

Im Rahmen der Presseaussendung lobt Espressif – wie in der Abbildung gezeigt – die diversen Sicherheitsfunktionseinheiten, die dem C6 das Erfüllen der durchaus stringenten Kriterien erfüllen.

Bildquelle: https://www.espressif.com/en/news/C6_PSA_Level2

Interessant ist an der Ankündigung auch der „Hat Tip“ in Richtung von ESP-TEE – dabei handelt es sich um eine besondere Ausführungsumgebung, die eine Art virtuelle Maschine zur Isolation von sicherheitskritischen Code ermöglicht.

ESP32-C2 / ESP8684 – neue Hardwarerevision mit mehr Speicher.

Der C2 basiert ebenfalls auf einem RISC/V-Kern und ist per se seit einiger Zeit bekannt. Im Rahmen einer PCN kündigte Espressif nun an, Erweiterungen an der Hardware vorgenommen zu haben.

In der PCN findet sich spezifischerweise die folgende Passage, die auf die Erweiterungen im Bereich des zur Verfügung stehenden Speichers eingehen:

1 |

The modification to the ESP32-C2 series chip described in Para 1 involves a hardware metal layer |

2 |

change, with the chip version being upgraded from v1.2 to v2.0. The latest ESP32-C2 v2.0 chip, when |

3 |

used with the updated ESP-IDF, provides approximately 20 KB of additional SRAM and around 100 |

4 |

KB of extra flash memory for project development (actual gains may vary depending on the specific |

5 |

application). Since the modules and development boards listed in Para 1 use the ESP32-C2 series |

6 |

chip, they have also been updated accordingly. |

7 |

2

|

8 |

The ESP8684H4 and ESP8684H4X chip mentioned in Para 1 has introduced a new in-package flash |

9 |

as an alternative source to improve supply stability. As a result, the corresponding modules and |

10 |

development boards listed in Para 1 have also been updated accordingly. |

11 |

--- via https://www.espressif.com/en/news/ESP32_C2_Upgrade |

Zu beachten ist, dass die V2-Varianten der Chips nicht „eins zu eins“ mit den bekannten Varianten kompatibel sind – neben einer Änderung in der Applikationssoftware ist es auch erforderlich, die neuen Bestellnummern zu nutzen.

SiFive HiFive Premier P550 – Ubuntu-Performance im Test

RISC/V-Rechenkerne kommen nicht nur im Mikrocontroller zum Einsatz. SiFive bietet seit längerer Platinen auf Basis der hauseigenen Prozessoren an, um Linux-Entwickler zur Interaktion mit der neuen ISA zu animieren.

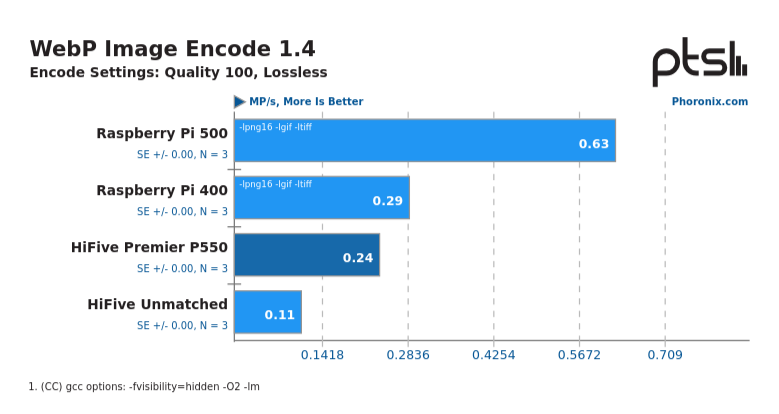

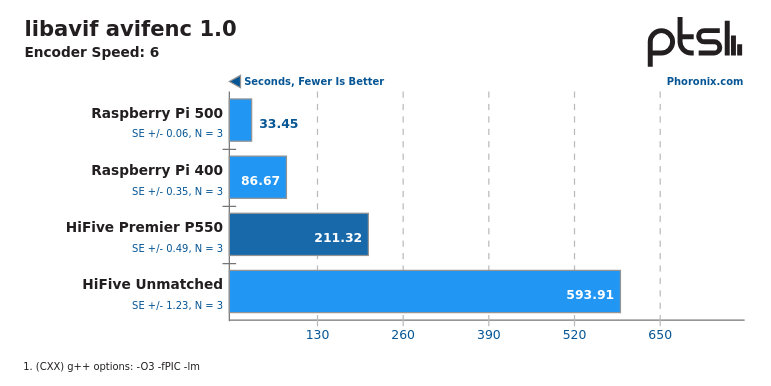

Im Hause Phoronix konnte man eine neue Variante erbeuten, und testete sie – wie erwartet – im Bereich der Performance. Neben einem älteren RISC/V-Board kamen auch verschiedene Raspberry Pis zum Einsatz – im Allgemeinen gilt leider nach wie vor, dass selbst das Vorgänger-Modell der Uptoniten dem Neuling im Bezug auf die Performance überlegen ist:

1 |

The SiFive HiFive Premier P550 tended to be multiple times faster than the HiFive Unmatched. The performance relative to the Raspberry Pi 4 and Raspberry Pi 5 ARM SBCs varied but in some workloads the SiFive P550 was outperforming the Raspberry Pi 4 (400). |

Betrachtet man die Ergebnisse im Detail, so ist der Nachteil von Situation zu Situation unterschiedlich. In manchen Benchmarks kann der Kern gut mithalten, während er in anderen absolut hoffnungslos unterlegen ist.

Bildquelle: https://www.phoronix.com/review/sifive-hifive-premier-p550

Bildquelle: https://www.phoronix.com/review/sifive-hifive-premier-p550

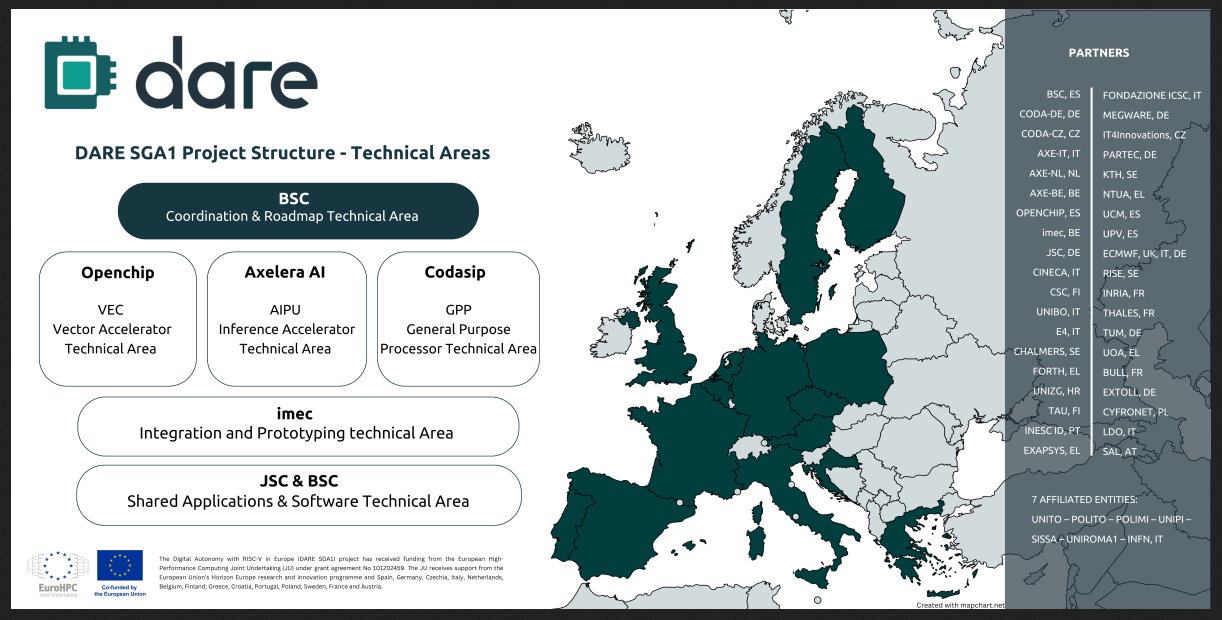

DARE – oder-EU Kommission ihr Hauptprozessor

Dass die EU im Gutteil der technologischen Weiterentwicklung eine weit abgeschlagene Position einhält, wird von anderen Kolumnisten seit Jahrzehnten erfolgreich beackert. Mit dem DARE-Projekt möchte die EU-Kommission nun zumindest bis zu einem gewissen Grad gegensteuern.

Bildquelle: https://dare-riscv.eu/launch-of-dare-sga1-project/.

Die Zieldefinition des mit 240 Millionen Euro dotierten Projekts ist dabei folgendermaßen beschrieben:

1 |

By the end of its first phase, DARE SGA1 will lay the groundwork for Europe’s first fully European HPC system, fostering technological self-reliance and ensuring that European industry, research, and society at large can benefit from secure, high-performance, and energy-efficient computing solutions. |

Spezifischerweise ist die Entwicklung von drei Chiplets auf Basis der RISC/V-Technologie geplant:

1 |

• Vector accelerator (VEC) for high-precision HPC and emerging applications in the HPC-AI convergence domain, led by Openchip |

2 |

• AI Processing Unit (AIPU) designed for AI inference acceleration in HPC applications, led by Axelera AI |

3 |

• General-purpose processor (GPP) optimized for HPC workloads in European supercomputers, led by Codasip |

China – Regierungsanweisung für RISC/V dürfte unmittelbar bevorstehen

Chinesische Unternehmen wie GigaDevice haben die RISC/V-Architektur durchaus aktiv promoted. Reuters berichtet unter https://www.reuters.com/technology/china-publish-policy-boost-risc-v-chip-use-nationwide-sources-2025-03-04/ darüber, dass bald eine Regierungsanweisung zur Nutzung des Systems ante Portas steht:

1 |

It is being drafted jointly by eight government bodies, including the Cyberspace Administration of China, China's Ministry of Industry and Information Technology, the Ministry of Science and Technology, and the China National Intellectual Property Administration, they added. |

Wer eine Zusammenfassung chinesischer Aktivitäten im Bereich RISC/V begehrt, findet unter https://www.theregister.com/2025/03/05/china_alibaba_risc_v_c930/ eine Zusammenstellung.

OnSemi will Allegro kaufen

Die große Politik beschränkt sich nicht nur auf den Tjost um die korrekte Architektur. Im Halbleiterbereich steht eine Übernahme ante Portas – OnSemi legt abermals nach, um Allegro Microsystems übernehmen zu können.

In einer vor wenigen Stunden versendeten Pressemitteilung findet sich die folgende Passage:

1 |

onsemi (NASDAQ: ON) today disclosed details of a proposal submitted to the Board of Directors of Allegro MicroSystems, Inc. ("Allegro") (NASDAQ: ALGM) to acquire the company for $35.10 per share in cash for each share (the “Proposal”) of Allegro’s common stock on a fully diluted basis at an implied enterprise value of $6.9 billion. |

Lesestoff: Nutzung von eSIMs unter Linux.

Wer sich mit dem Design von Funkmodulen auseinandersetzt, ist mit Sicherheit bereits über den Begriff der eSIM gestolpert. Der schwedische Funkmodul-Distributor TechShip bietet unter der URL https://techship.com/blog/how-to-use-an-esim-in-linux-7/ nun ein durchaus lesenswertes Tutorial an, das die Inbetriebnahme und Interaktion zwischen Linux-Hosts und virtualisierter SIM-Karte beschreibt.

Zuerst erschienen bei Mikrocontroller.net News

Quelle: Weiterlesen